AVE (ASTC AMS Verification Environment): Application Brief

Fast Functional Verification of Mixed Analog and Digital SoCs: Application Brief

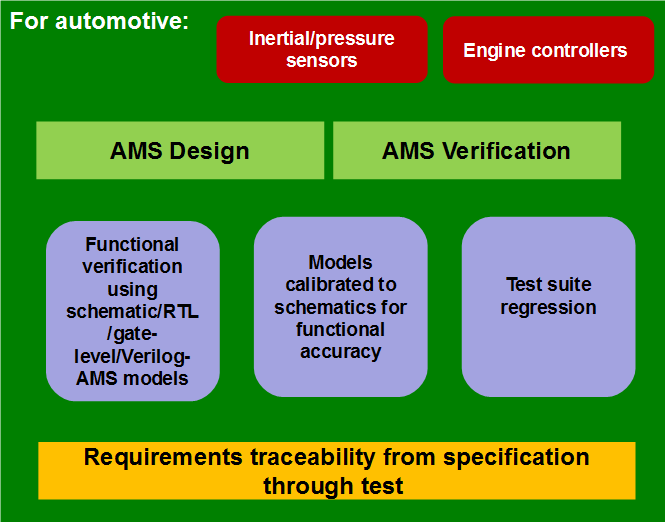

Analog / Mixed Signal: Automotive

In automotive, ASTC delivered design and verification of:

- Inertial/pressure sensors

- Engine controllers design and verification

- Mixed-signal functional verification using schematic/RTL/gate-level/Verilog-AMS models

- Verilog-AMS models calibrated to schematics for functional accuracy

- Automated test suite regression

As well as requirements traceability from specification through to test results.

Analog / Mixed Signal: Verification of Power Management ICs

Verification of power management ICs: Chip level verification using VVW (Verilog Virtual Wires.)

Simulation of over 10 ICs typically identified 80 bugs for new designs and 20-30 for derivatives.

Mixed approach satisfied different verification objectives:

- Full transistor simulations with schematic/AMS models.

- VVW for analog/digital boundary verification.

- Digital simulations for digital unit test.

- Traceability of verification requirements through test results.

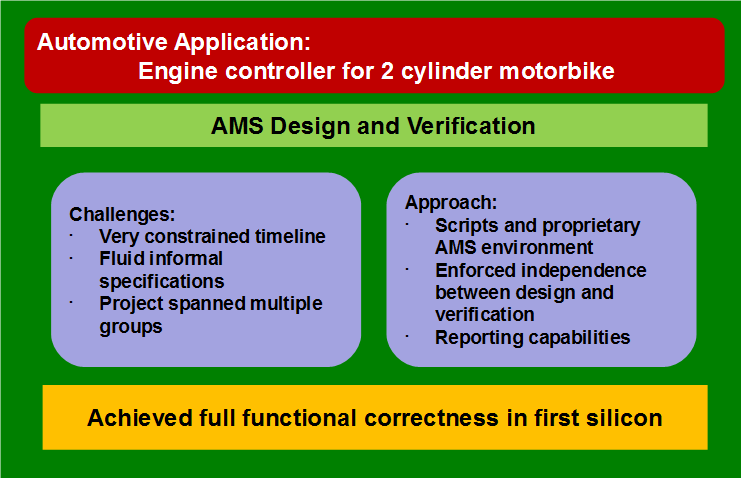

Analog / Mixed Signal: Engine Controller Design and Verification

Application: automotive engine controller for a 2 cylinder motorbike.

ASTC did AMS design and verification, on a very constrained timeline, with fluid informal specifications. Project spanned several different groups: scripts and proprietary AMS environment enforced independence between design and verification, with reporting capabilities.

Achieved full functional correctness in first silicon.

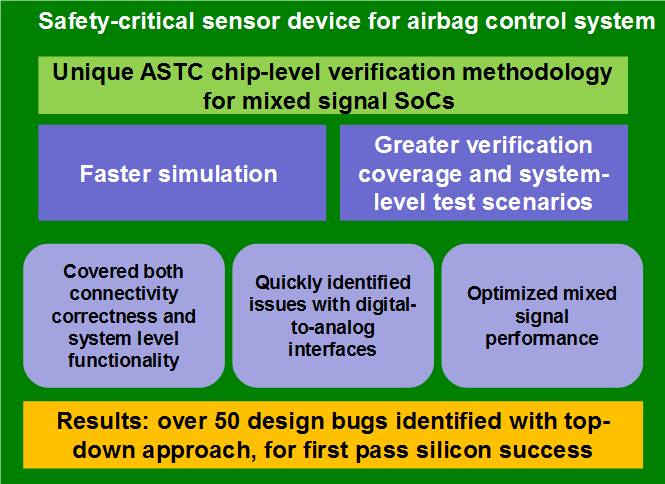

Analog / Mixed Signal: Chip-level Verification for Automotive

Application: safety-critical sensor device for airbag control system.

ASTC developed a chip-level verification methodology for mixed signal SoCs that provides significant improvements in simulation performance, compared with traditional approaches, for greater verification coverage and system-level test scenarios, with less simulation time required to cover both connectivity correctness and system level functionality.

ASTC verification supports top-down design to quickly identify issues with digital-to-analog interfaces and ensure optimal mixed signal design and performance. More verification coverage and system-level test scenarios, with less simulation time for system functionality and connectivity

ASTC top-down verification quickly identified issues with digital-to-analog interfaces and optimized mixed signal performance

Results: over 50 design bugs were identified that would not have been found without the top-down approach, for first pass silicon success.