Intelligent Sensor and Power Management Platform of ASIC IP for Sensor, Power, and IoT Applications

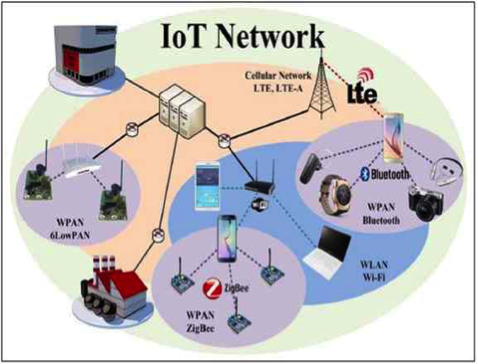

As falling silicon technology node-size continues to reduce the power consumption and physical space required for any given ASIC design, whole new embedded ASIC application areas continually open up. Nowhere has this trend been more obvious than in the world of sensor-based, intelligent, connected embedded applications.

|

|

A key challenge with this growing diversification is the apparent conflict between adding new features vs. reducing product costs, development costs, and getting product to market sooner. Historically, product development teams have had to pick one or the other, but today the market is demanding nearly all: to be competitive requires a product to be available sooner, with more new features, and delivered at lower cost, with higher quality.

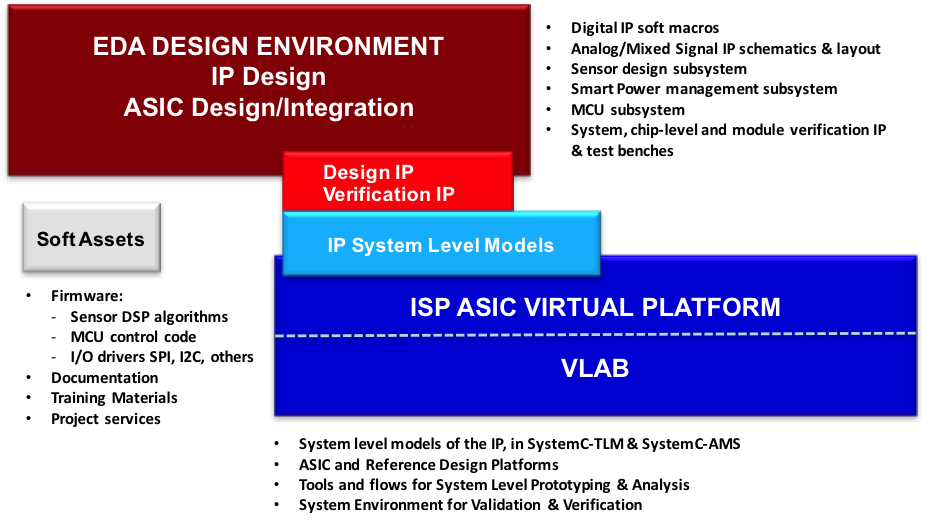

ASTC is helping its customers tackle this challenge with a comprehensive, platform based approach: the Intelligent Sensor and Power Management Platform (ISP). This comprises:

- Design building blocks,

- Pre-assembled and pre-validated sub-systems,

- Supporting tools and environments.

With ISP, ASTC enables a project for a new ASIC to be executed within the cost budgets and time lines of an ASIC derivative project.

When integrated together into a design platform for the rapid development of new ASICs and associated software, a wide range of advanced, market-leading applications in intelligent sensors, control, and IoT can be now be developed much more efficiently, and fielded more quickly.

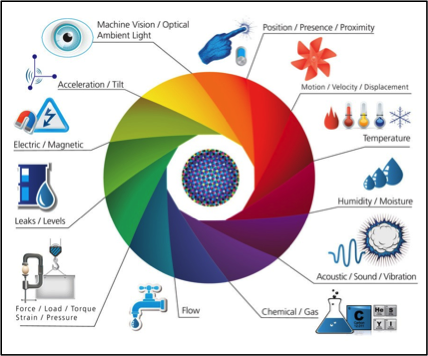

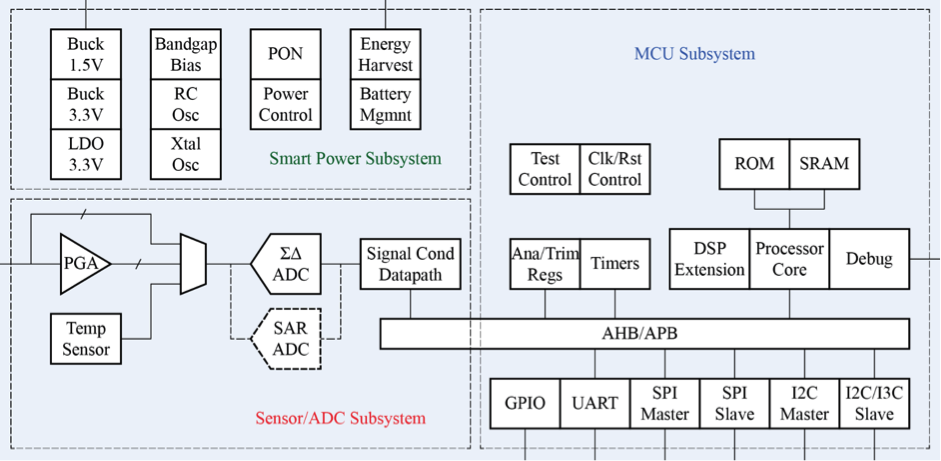

At the top-most level, the ISP provides IP, subs-systems, and solutions, which address three common challenges in the design of very low power, embedded sensing devices:

- Power management and energy harvesting for low power, long battery life applications (including no battery applications);

- Sensor-interfacing analog front ends, and signal processing;

- Software programmable control, communications, and processing.

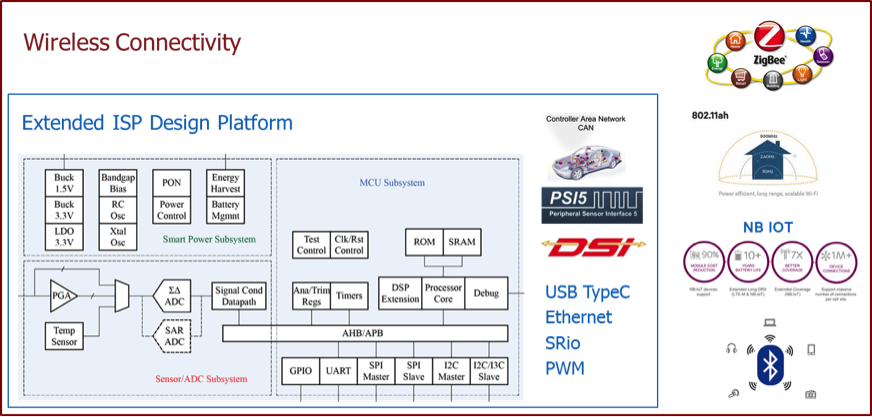

Together, the ISP sub-systems and their building blocks provide a comprehensive design suite for a wide range of embedded applications. The industry-standard block interfaces used by ISP enable other new customer or third-party design blocks to be easily added and interfaced to the rest, allowing for easy expandability to cover additional requirements such as device to device wired or wireless communications and security.

Depending on project requirements, ISP supports different options for the integrating an MCU core and for other I/O IP, including:

| MCU Core options: | I/O Components: |

| ARM Cortex-M0 and Cortex-M4 | USB controller and transceiver |

| RISC-V | Digital frequency synthesizer |

| ColdFire V1 | Audio pulse-width modulation |

| 8051 | LED/LCD drivers |

Energy management for low power consumption is one of the most critical aspect of almost every embedded device, especially battery powered devices, such as IoT devices in the field. In order to maximise efficiency in any given application, a range of power management techniques typically need to be applied. The ISP Smart Power Subsystem controller provides for a configurable and flexible power management system, delivering a range of different power modes in order to serve the widest possible set of operational requirements:

- Ultra-low power shutoff mode

- Stop mode, including power-on-reset, RAM and CPU retention

- Hibernate mode, including power-on-reset, RAM and CPU retention

- Sleep mode, with fast wakeup

- Standard run mode, with code executed from flash

In order to support the needs of projects looking for help at the component level, ASTC also makes available a number of the ISP elements as standalone design IP, applicable to any embedded application. These include:

Digital IP

- RISC-V Core Platforms

- RV32EC_P2 Processor Core IP – 2-stage pipeline RISC-V processor core, to meet the needs of small, low-power embedded applications, running only trusted firmware.

- RV32IC_P5 Processor Core IP – 5-stage pipeline core RISC-V processor, to meet the needs of medium-scale embedded applications that require higher performance, cache memories, and running a mix of trusted firmware and user application code

- RISC-V Timer – suite of timers conforming to RISC-V standard machine timer specifications

- RISC-V Platform-Level Interrupt Controller – configurable interrupt controller conforming to the RISC-V PLIC specification, for use in systems with a large number of interrupt sources and multiple processor targets for interrupt delivery.

- 8051 Core Platform

- Optional timer and port peripherals

- Optional APB bridge for memory-mapped I/O

- Optional debug controller accessed via a JTAG TAP for in-system debug

- Optional DSP coprocessor for signal processing applications

- I3C Slave Core

- Provides a slave interface for the following protocols:

- I2C standard mode (100kbps)

- I2C fast mode (Fm, 400kbps) and fast-mode plus (Fm+, 1Mbps)

- I2C high-speed mode (3.4Mbps)

- I3C single data rate (SDR up to 12.5Mbps)

- Provides a slave interface for the following protocols:

- I2C Slave & Master

- SPI Slave & Master

Analog/Mixed Signal IP

- 1.8 GHz Phase-Locked Loop

- Optimized design with very low clock jitter for a high speed serializer data transmitter, suitable for high speed SERDES.

- LDO Regulators

- 1.5V and 3.3V regulators

- 10 bit SAR ADC

- Optimized for ultra-low power, 100kHz sampling.

- Temperature Sensor

- On-chip temperature monitoring and ambient temperature estimation

- RF Energy Harvester and Rectifier

- Designed to absorb 900MHz RF energy and converts to the DC voltage form with a rectifier. The RF rectifier unit is based on the Dickson charge pump.

- Oscillators

- 48MHz RC Oscillator

- Low Power 10KHz Oscillator

- PGA

- Differential rail-to-rail input and differential rail-to-rail output.

- Selectable 32 gain levels, and contains a voltage reference circuit which can be externally connected to the amplifier inverting input for sensor applications.

ISP Extensions and Connectivity

The ISP Design Platform includes the core subsystems that form the basis of any new embedded design, and supports connectivity and application-specific blocks and extensions via open, standard, interfaces. This enables easy integration with new project- or application-specific design blocks or third-party IP, which may be required by any connected embedded or IoT device:

ISP Virtual Platform

VLAB Environment for Rapid Virtual Prototyping and Software Development

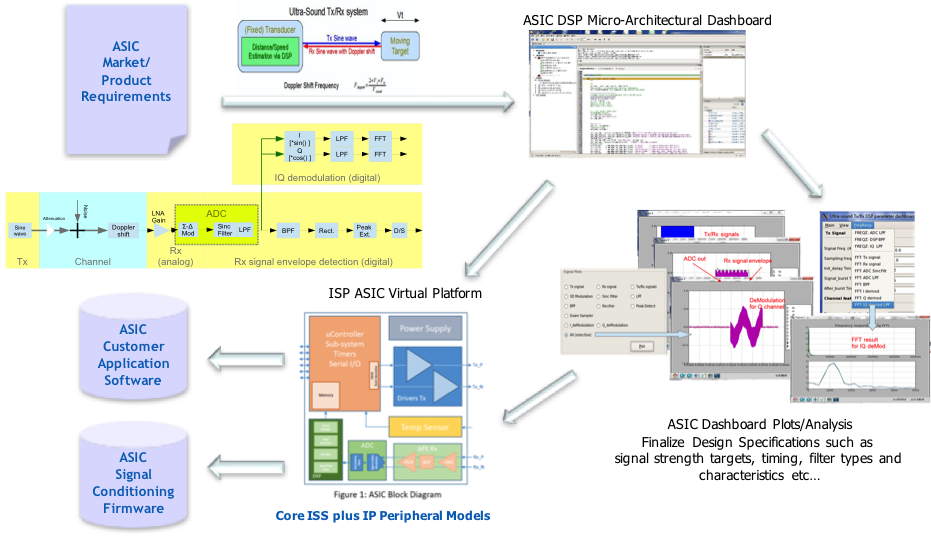

To support the rapid prototyping of new ISP IP and ISP ASIC applications, including the development of application code in a virtual, all-in-software environment, ASTC provides an ISP virtual platform and prototyping environment in VLAB, comprising:

- Models of all IP, including a library of SystemC/TLM models of included IP blocks

- CPU ISS models, fast timing-annotated, Instruction Set models of RISC-V, ARM Mx, and 8051

- Pre-assembled Virtual ASIC models and platforms

- Models of IO, devices, and system test bench components

- Tools for hardware rapid virtual prototyping, test, debug, and performance analysis, for new:

- IP modules,

- CPU ISA modifications and extensions,

- Hardware accelerators,

- ASICs, devices, and networks.

- Tools for software development, debug, test, and performance analysis

ISP customers can rapidly prototype a new ASIC, including any required new IP. Users can assemble a system level test-bench, connect to simulated or real IO signals and sources, run realistic functional or performance scenarios, and analyse collected data in order to optimise their ASIC design and associated software. The overall design and specification of the ASIC can be validated, and crucially the project can demonstrate the new virtual ISP ASIC to their customers and partners, ensuring that all parties rapidly converge on an agreed and complete set of requirements before committing to detailed design, prototyping, and manufacture.

By combining high-value design IP alongside a comprehensive virtual IP platform, the ISP therefore becomes an enabler of commercially successful development of new, challenging IoT applications. Silicon and software architects can now collaborate fully, both working on the same platform, at the same time. Furthermore, the virtual ISP ASIC environment itself evolves over time, constantly reflecting the latest state of the emerging hardware design. Subsequently, application teams can then use the same virtual platform for their broader software development work, allowing them the freedom to write production-ready code. As a result, by the time the real hardware is available, that application stack has already been thoroughly tested and integrated, with multiple iterative builds along the way ensuring that the delivered functionality meets or exceed all design specifications.

ISP ASIC Consulting Services

ASTC supports customers of ISP with an extensive body of experience in ASIC design and related software development and validation activities, spanning markets as diverse as safety critical and consumer driven, including for such applications as:

| Safety Critical/High Reliability: | Consumer Product Design/Verification: |

| System Basis Chips for automotive | IoT and capacitive touch sensors |

| Crash impact safety, electronic braking | Codec, Bluetooth, and Wi-Fi design |

| Analogue engine control devices | Multi-core platform design/integration |

| Implantable medical devices | SerDes plus high-speed PLL & drivers |

| LiON battery management | Digital asynchronous high speed design |

| Automotive environmental monitoring | Regulator design and verification |

| Parking assist and “blind spot” ASICs | Network processors |

| Airbag control ASICs | Power management IC verification |

| Industrial microcontrollers |

For more information on ASTC’s unique range of ISP related products and services supporting embedded silicon and software design, please contact us.